# NVIDIA JETSON TX1 PCIe COMPLIANCE TESTING REFERENCE

DA-09103-001\_v1.0 | August 2018

## **DOCUMENT CHANGE HISTORY**

#### DA-09103-001\_v1.0

| Version | Date            | Description of Change |

|---------|-----------------|-----------------------|

| 1.0     | August 22, 2018 | Initial Release       |

## **TABLE OF CONTENTS**

| Overview                                            | 1 |

|-----------------------------------------------------|---|

| Equipment                                           | 2 |

| Test Fixtures                                       |   |

| Oscilloscope                                        | 3 |

| PCIe Gen1                                           |   |

| PCIe Gen2                                           |   |

| Probes                                              |   |

| Cables                                              |   |

| Termination Load/Adapter                            |   |

| Software                                            |   |

| Setup Example                                       |   |

| CEM 2.0 Measurements Using Tektronix Scope TDS61X4C |   |

| Debugging                                           |   |

| If PCI Express Does not Work                        |   |

| Device Fails at ASPM LO/L1 Enabled                  |   |

## **LIST OF FIGURES**

| Figure 1. | Setup Example          | , 9 |

|-----------|------------------------|-----|

| Figure 2. | Power Sequence Diagram | 11  |

## **LIST OF TABLES**

| rable 1. | Partial List of Pule Test Fixtures        | . ა |

|----------|-------------------------------------------|-----|

| Table 2. | Partial List of Instruments for PCIe Gen1 | . 4 |

| Table 3. | Partial List of Instruments for PCIe Gen2 | . 4 |

| Table 4. | Partial List of Probes                    | . 5 |

| Table 5. | Partial List of Cables                    | . 5 |

| Table 6. | Partial List of Termination Load/Adapter  | . 6 |

| Table 7. | Recommended Test Software                 | . 8 |

## **OVERVIEW**

NVIDIA® Jetson™ TX1 includes the Peripheral Component Interconnect Express (PCIe) interface. The implementation in Jetson TX1 supports both 2.5 G (PCIe Gen1) and 5.0 G (PCIe Gen2) transfer rates.

This application note describes the test equipment, software, and setup required to run the PCI Express (PCIe) Gen1 and Gen2 electrical compliance tests. The Jetson TX1 has been tested under worst case scenarios and the hardware can adapt to the compliant devices and channel automatically. The hardware calibrates the termination impedance for both PCIe transmitter and receiver, and the receiver adapts its internal parameters to optimize signal characteristics. The hardware is designed to directly work with compliant devices and compliant channels automatically. Therefore, no tuning will be required if customer designs follow the routing guidelines published in our design guide.

The lane mappings for the configurations are internal to the PCIe root port controller. For the supported configurations, refer to the OEM product design guide for Jetson TX1.

# **EQUIPMENT**

The components required to perform PCIe compliance testing include:

- ► Test Fixture

- ▶ Oscilloscope

- ▶ Probe

- ▶ Cables

- ► Termination Load/Adapter

- Software

- PCI-SIG Clock Jitter Tool

- SigTest 3.2.0

There are many tools currently available to help with compliance testing. The following sections list some of the equipment available. Items marked with an asterisk (\*) indicate equipment that NVIDIA has used in its testing.

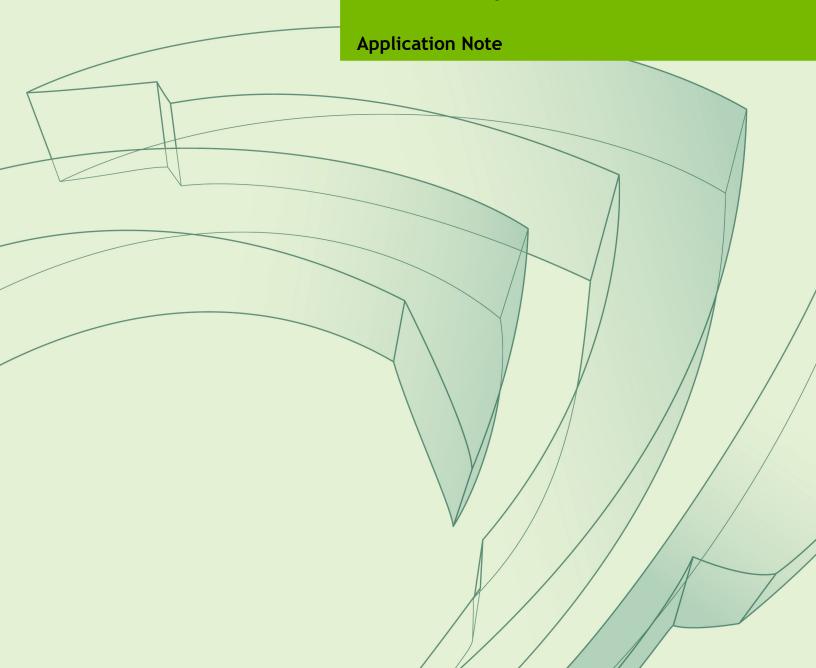

### **TEST FIXTURES**

Test fixtures are used to connect the probes to the TX pins of the PCIe interface. Fixtures of different interface types are available and are recommended over using adapters to convert the interface type. Whichever fixture is selected, it must have SMP interconnects to avoid impedance mismatches due to discontinuities.

Table 1. Partial List of PCIe Test Fixtures

#### Notes:

CLB is Revision 2.0 Compliance Board.

There are two different versions of CLB:

- •x1/x16 which has x1 and x16 card edges for testing x1 and x16 motherboard slots

- •x4/x8 which has x4 and x8 card edges for testing x4 and x8 motherboard slots

The compliance load board (CLB) version(s) needed for testing a motherboard depend on the slot widths on the motherboard. All slots on the motherboard must be tested. Ordering information for the CLB can be found on PCI-SIG website at: http://pcisig.com/pci-express-compliance-load-board-clb

### **OSCILLOSCOPE**

An oscilloscope is used to measure the signals.

#### PCle Gen1

For PCIe Gen1, the PCIe specification requires that the oscilloscope have at least 6 GHz of bandwidth.

Table 2. Partial List of Instruments for PCIe Gen1

| Company    | Product                    | Image and Description |

|------------|----------------------------|-----------------------|

| Tektronix* | TDS6604B<br>or better      |                       |

| Agilent    | DSO/DSA91304A<br>or better |                       |

### PCle Gen2

For PCIe Gen2, the PCIe specification requires that the oscilloscope have at least 12 GHz of bandwidth.

Table 3. Partial List of Instruments for PCIe Gen2

| Company    | Product                | Image and Description |

|------------|------------------------|-----------------------|

| Tektronix* | DSA71254<br>or better  |                       |

| Agilent    | DSO81304B<br>or better |                       |

## **PROBES**

Probes are used to connect the oscilloscope to the test fixture; oscilloscope probes must be a minimum of 8 GHz of bandwidth.

Table 4. Partial List of Probes

| Company    | Product                                | Image and Description |

|------------|----------------------------------------|-----------------------|

| Tektronix* | 1169A<br>Requires<br>Agilent<br>N5380A |                       |

## **CABLES**

Cables are used to measure signal quality.

Table 5. Partial List of Cables

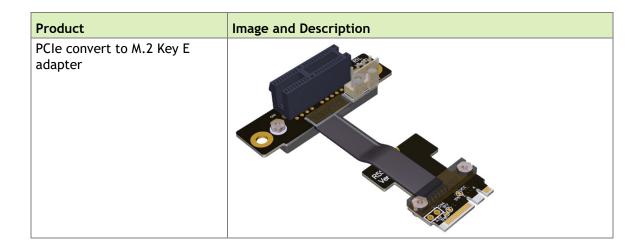

## TERMINATION LOAD/ADAPTER

The following table is a list of termination load/adapters.

Table 6. Partial List of Termination Load/Adapter

| Product                  | Image and Description |

|--------------------------|-----------------------|

| 50 Ohm Termination Load* |                       |

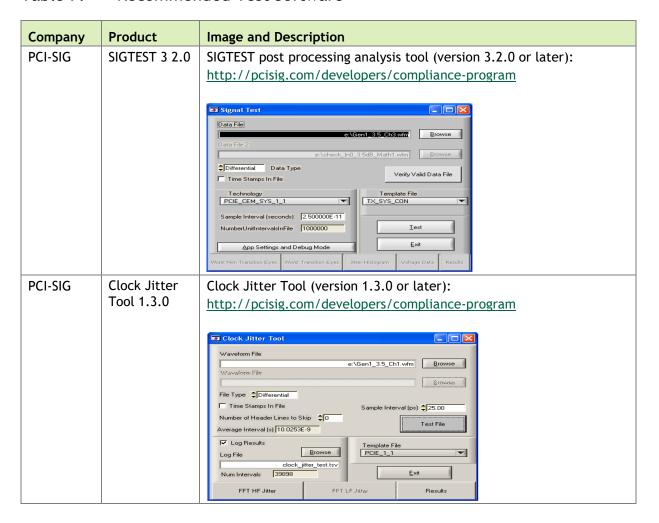

## **SOFTWARE**

Use of official compliance test software is recommended, but not required. While manually measuring the signal might be just as effective, it must ultimately pass with the compliance software at the compliance house.

Recommended Test Software Table 7.

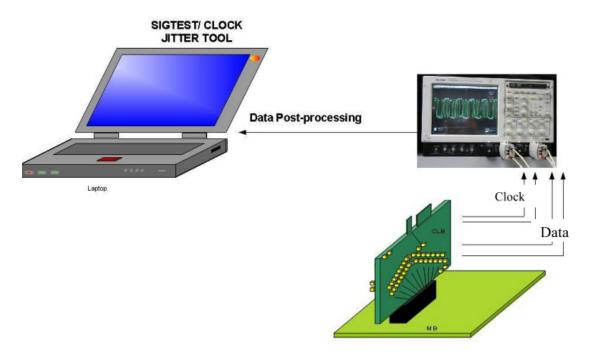

# SETUP EXAMPLE

The following figure is an example of a testing setup.

Figure 1. Setup Example

#### Notes:

- 1. Post processing tools Sigtest and Clock Jitter Tool can also be run on the scope.

- 2. Problem with reference. If system shows "in Error! Reference source not found." Both reference clock and data lane under test must both be sampled simultaneously to carry out measurements as described in the PCI Express Card Electromechanical Specification Revision 2.0.

# **CEM 2.0 MEASUREMENTS USING TEKTRONIX SCOPE TDS61X4C**

PCI-SIG provides the compliance standards and test descriptions for system boards and add-in cards that comply with PCI Express Card Electromechanical Specification Revision 2.0. Customers should refer to the document for an overview of the tests that are performed to check the compliance criteria. Depending on the brand of equipment being used for the test, customers can then refer to the manufacturer's documentation for stepby-step procedure to perform the test.

PCI Express specification require devices to have a built-in mechanism for testing the electrical characteristics. Therefore, when the transmit lanes of the device are terminated with a 50-ohm load, the transmit lanes will automatically be forced into compliance mode.

# **DEBUGGING**

High speed I/O design is difficult to debug and will get harder as speeds increase. The following are a few common PCI Express issues.

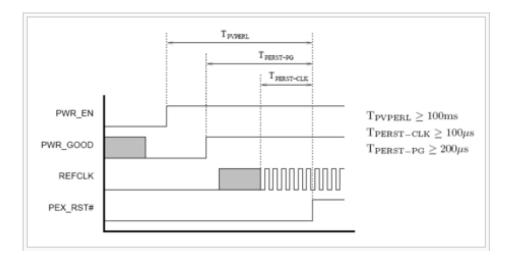

### IF PCI EXPRESS DOES NOT WORK

If PCI Express does not respond or no signals are being sent out, verify the following:

- Check the applied power for expected value.

- Check that clocks are on.

- Check for chip reset de-assertion.

- Check the power sequencing.

Figure 2. Power Sequence Diagram

## DEVICE FAILS AT ASPM LO/L1 ENABLED

Connect device to a PCIe bus analyzer (for example, LeCroy Protocol Analyzer) to assist with the debug.

- 1. Configure analyzer to trigger on root repeatedly sending PM\_Request\_Ack DLLPs.

- 2. Capture the bus traffic at the time the bus failure occurs.

#### Notice

The information provided in this specification is believed to be accurate and reliable as of the date provided. However, NVIDIA Corporation ("NVIDIA") does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information. NVIDIA shall have no liability for the consequences or use of such information or for any infringement of patents or other rights of third parties that may result from its use. This publication supersedes and replaces all other specifications for the product that may have been previously supplied.

NVIDIA reserves the right to make corrections, modifications, enhancements, improvements, and other changes to this specification, at any time and/or to discontinue any product or service without notice. Customer should obtain the latest relevant specification before placing orders and should verify that such information is current and complete.

NVIDIA products are sold subject to the NVIDIA standard terms and conditions of sale supplied at the time of order acknowledgement, unless otherwise agreed in an individual sales agreement signed by authorized representatives of NVIDIA and customer. NVIDIA hereby expressly objects to applying any customer general terms and conditions with regard to the purchase of the NVIDIA product referenced in this specification.

Unless specifically agreed in writing by NVIDIA, NVIDIA products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of the NVIDIA product can reasonably be expected to result in personal injury, death or property or environmental damage. NVIDIA accepts no liability for inclusion and/or use of NVIDIA products in such equipment or applications and therefore such inclusion and/or use is at customer's own risk.

NVIDIA makes no representation or warranty that products based on these specifications will be suitable for any specified use without further testing or modification. Testing of all parameters of each product is not necessarily performed by NVIDIA. It is customer's sole responsibility to ensure the product is suitable and fit for the application planned by customer and to do the necessary testing for the application in order to avoid a default of the application or the product. Weaknesses in customer's product designs may affect the quality and reliability of the NVIDIA product and may result in additional or different conditions and/or requirements beyond those contained in this specification. NVIDIA does not accept any liability related to any default, damage, costs or problem which may be based on or attributable to: (i) the use of the NVIDIA product in any manner that is contrary to this specification, or (ii) customer product designs.

No license, either expressed or implied, is granted under any NVIDIA patent right, copyright, or other NVIDIA intellectual property right under this specification. Information published by NVIDIA regarding third-party products or services does not constitute a license from NVIDIA to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property rights of the third party, or a license from NVIDIA under the patents or other intellectual property rights of NVIDIA. Reproduction of information in this specification is permissible only if reproduction is approved by NVIDIA in writing, is reproduced without alteration, and is accompanied by all associated conditions, limitations, and notices.

#### ARM

ARM, AMBA and ARM Powered are registered trademarks of ARM Limited. Cortex, MPCore and Mali are trademarks of ARM Limited. All other brands or product names are the property of their respective holders. "ARM" is used to represent ARM Holdings plc; its operating company ARM Limited; and the regional subsidiaries ARM Inc.; ARM KK; ARM Korea Limited.; ARM Taiwan Limited; ARM France SAS; ARM Consulting (Shanghai) Co. Ltd.; ARM Germany GmbH; ARM Embedded Technologies Pvt. Ltd.; ARM Norway, AS and ARM Sweden AB.

#### Trademarks

NVIDIA, the NVIDIA logo, and Jetson are trademarks and/or registered trademarks of NVIDIA Corporation in the U.S. and other countries. Other company and product names may be trademarks of the respective companies with which they are associated.

#### Copyright

© 2018 NVIDIA Corporation. All rights reserved.